1 科研动态

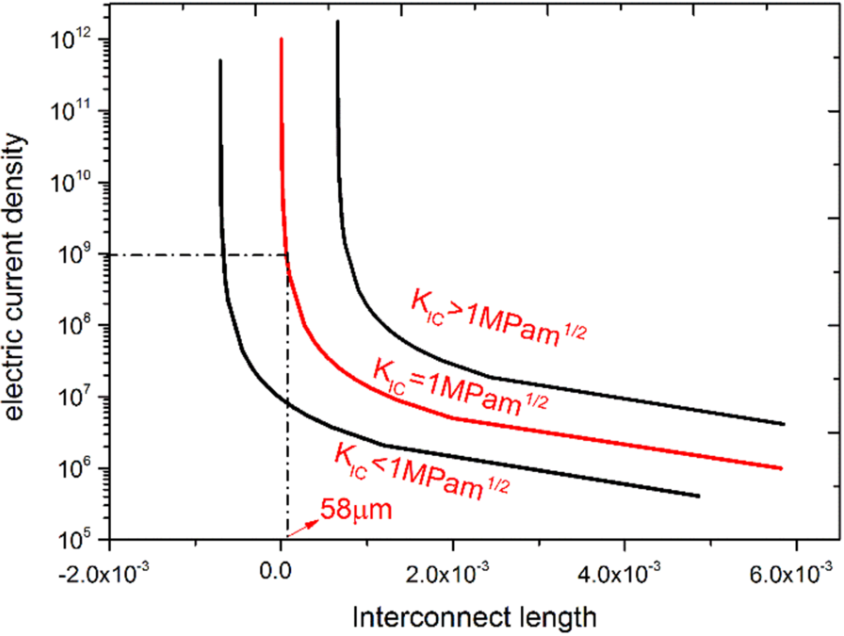

1、J. Electron. Packaging:铜互连的电迁移引起的界面断裂

电迁移定义为导电电子和扩散金属原子之间的动量转移,可导致导电材料中质量的积累和耗尽,最终导致在导体的阴极和阳极端形成空隙或小丘。值得注意的是,集成电路的小型化增加了电流密度,从而加剧了电迁移的影响,使其成为微电子器件故障的最主要原因之一。

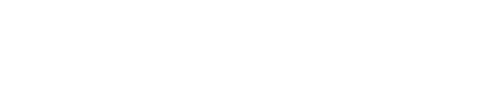

近日,中国工程物理研究院等机构的研究人员采用连续位错模型来确定铜线内外界面质量扩散引起的应力场,深入研究了由电迁移引发的铜/电介质界面(特别是在铜互连的阳极端)开裂的失效模型。研究发现除了阴极或阳极侧的预期拉伸或压缩应力之外,还在介电层和铜线的阳极端之间的界面处识别出异常应力奇异性。并且理论预测与实验数据吻合良好,这种奇异的应力分布在电迁移的影响下导致阳极端的介电层的压缩部分中的裂纹。该研究提出了一种类似于断裂力学中应力强度因子的新型失效准则。该文章以“Interfacial Fracture Caused by Electromigration at Copper Interconnects”发表于J. Electron. Packaging上。

图1. 基于连续分布位错法的铜膜线与介质层界面电迁移的代表性模型

论文链接:https://doi.org/10.1115/1.4062828

2、J. Appl. Polym. Sci.:含有苯甲酰苯胺和芴单元的具有更优高温尺寸稳定性和低光学延迟的半脂环族透明聚酰亚胺薄膜的合成与表征

脂环族二酐和芳香族二胺制备的半脂环族聚酰亚胺薄膜作为一种在先进光电领域具有潜在应用前景的无色透明材料,近年来因其优异的综合性能而越来越受到人们的关注。

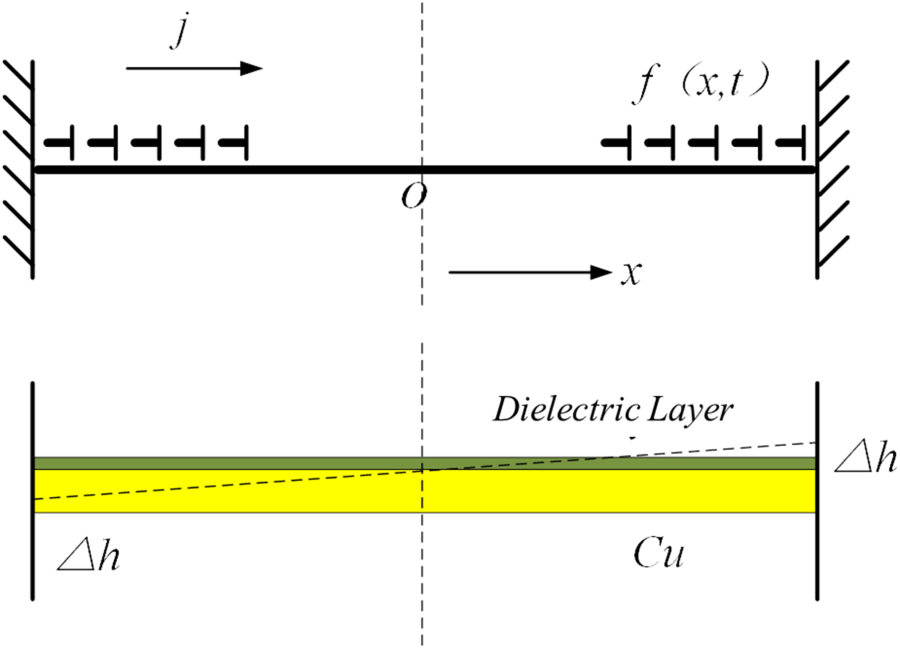

近日,中国地质大学等机构的研究人员制备了两种具有更优高温尺寸稳定性和低光学延迟的半脂环族透明聚酰亚胺薄膜PI-1(ccHPMDA-FDAADA)和PI-2(ctHPMDA-FDAADA)。二酐部分中的脂环环己烷单元赋予衍生的PI膜良好的光学透明性,刚性苯甲酰苯胺单元为PI膜提供了低的热膨胀系数(CTE),芴单元使PI膜具有良好的溶液可加工性和低的光学延迟(Rth)。两种PI薄膜的玻璃化转变温度均超过400°C,温度范围50 ~ 250°C时,CTE值分别为33.2 × 10−6/K(PI-1)和29.0 × 10−6/K(PI-2)。此外,PI薄膜在紫外-可见光区域表现出良好的光学透明度,在500 nm波长下,PI-1薄膜的透光率高于80%。PI-1和PI-2膜的平均折射率分别为1.6505和1.6485。PI膜的双折射值均低于0.01,导致低的光学各向异性,光学延迟(Rth)分别为77 nm(PI-1)和84 nm(PI-2)。该文章以“Synthesis and characterization of semi-alicyclic transparent polyimide films containing benzanilide and fluorene units with improved high-temperature dimensional stability and low-optical retardations”发表于J. Appl. Polym. Sci.上。

图2. 各PI薄膜的TMA曲线

论文链接:https://doi.org/10.1002/app.54732

3、IEEE T. Comp. Pack. Man.:用于封装屏蔽的低成本电磁吸波材料

控制电磁干扰(EMI)对于电路及设备的正常运行非常重要。通常,一种方法是使用金属屏蔽层来防止电磁辐射进入屏蔽层的另一侧,另一种方法则是使用电磁吸收器。

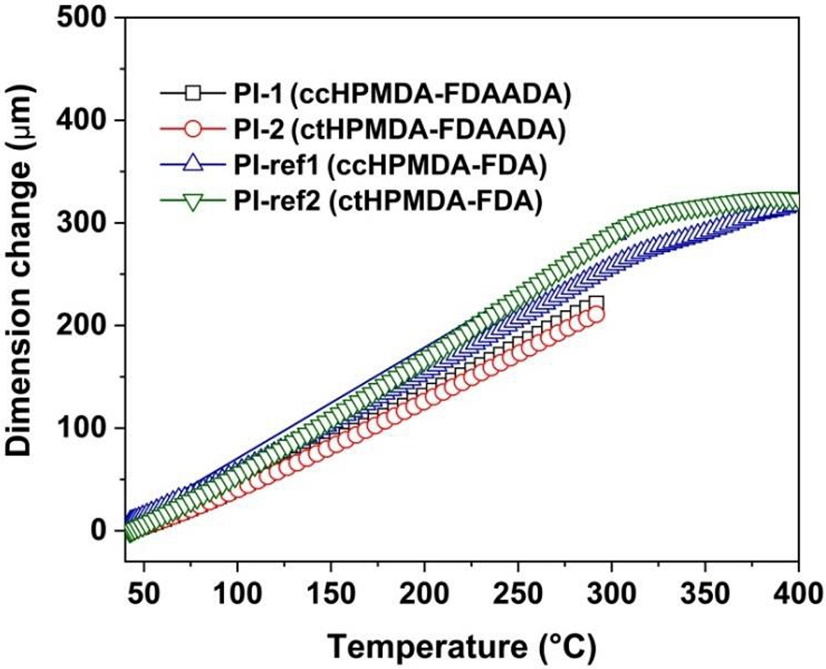

近日,印度比尔拉理工学院的研究人员提出了一种低成本的方案来解决封装结构的电磁干扰问题。吸收器由刻在丙烯酸片上的圆形频率选择表面(FSS)结构组成。吸收体结构的每个单元都填充有背衬接地铜箔的电介质材料,顶部覆盖有丙烯酸薄片。结果表明,吸收体在7.88至13.03 GHz的宽频率范围内具有90%以上的吸收率。对高频结构模拟器(HFSS)仿真工具进行了详细的参数研究,并开发了原型模型。最后,将模拟结果与实测结果进行了对比验证,显示出良好的一致性。该研究为吸收X波段EMI提供了一种可行的解决方案。该文章以“Low-Cost Electromagnetic Absorbers for Shield Packaging”发表于IEEE T. Comp. Pack. Man.上。

图3. 模拟得到的吸收、反射及交叉极化参数

论文链接:DOI:10.1109/TCPMT.2023.3265706

4、IEEE T. Comp. Pack. Man.:基于TSV的三维集成的可靠性问题:界面裂纹的影响

3D 封装技术对提高性能、降低成本和更好的信号完整性的需求导致了硅通孔(TSV)的发展。然而,TSV在热循环过程中,由于热膨胀系数(CTE)不匹配会产生不良的热机械应力,从而在TSV的界面层上引发微裂纹(通常称为界面裂纹)。

近日,印度纳亚赖布尔国际信息技术研究所的研究人员考虑界面裂纹的加热和冷却场景,首次对TSV电气特性不利影响因素进行了全面分析。研究人员设计了一个新颖的等效电路,包括故障建模以及串扰引起的延迟、功耗、能量释放率(ERR)和散射参数(S)方面的可靠性问题,考虑金属-氧化物-半导体(MOS)效应来模拟不同裂纹宽度下的通孔故障。使用基于CMOS的驱动负载设置,将所提出的电气模型用于分析串扰、功率和损耗,同时考虑加热和冷却模式。所获得结果的验证表明,散射参数的偏差约为2.5%,与实验数据非常吻合。该研究为具有某些界面裂纹的TSV在3D封装中保持可靠应用提供了可行性。提供了该文章以“Reliability Concerns of TSV-Based 3-D Integration: Impact of Interfacial Crack”发表于IEEE T. Comp. Pack. Man.上。

图4. 不同加热和冷却界面裂纹条件的S 参数比较

论文链接:DOI:10.1109/TCPMT.2023.3325222

2 技术动态

1、为混合键合(hybrid-bonding)做好准备

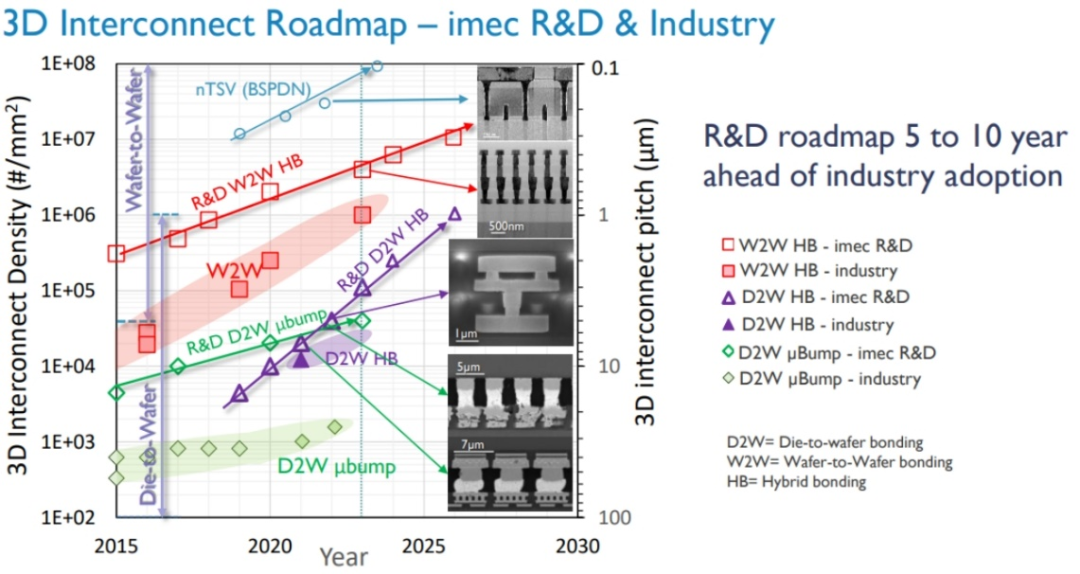

随着半导体行业将3D封装作为重点努力的方向,混合键合正成为实现3D异构集成的首选方法。

混合键合是指在一个键合步骤中同时键合电介质和金属焊盘,主要分为两种类型,一种是wafer-to-wafer键合,工艺更加成熟,缺点是仅适用于尺寸大小相同的芯片;另一种是die-to-wafer键合,涉及的工艺步骤更为复杂,比如其中将die单独放置在载体晶圆或玻璃上这一步骤就十分具有挑战性。

1.混合键合发展历程

混合键合于十多年前在CMOS图像传感器中首次亮相,由于NAND(闪存)阵列中的深沟槽蚀刻受限,3D NAND公司开始使用wafer-to-wafer混合键合。据镁光公司研发负责人介绍,用Cu-Cu键合取代HBM(高带宽存储器)内部的焊料,可以得到更细的间距、更薄的连接层厚度(BLT)和更牢固的接头。AMD是第一个采用混合键合将SRAM(静态随机存取存储器)堆叠在逻辑芯片上的公司。

目前wafer-to-wafer的键合占据主导地位,工艺处理更简单,缺陷控制更好,die-to-wafer的混合键合需要用到载体晶圆和有机胶层,因此热预算被限制在250℃以下。通过晶圆与晶圆(wafer-to-wafer)直接键合的方法将芯粒(chiplet)进行垂直堆叠,互连间距可以从微凸点工艺的35 µm缩小至10 µm或更细,同时也将信号延迟降低到可以忽略的水平,使更薄更小的封装体具有更快的内存/处理器速度和更低的功率消耗。

图5. die-to-wafer、wafer-to-wafer混合键合的互连间距分别可达到 1 μm和 0.5 μm

(来源:imec)

混合键合需要采用十分严格的工艺设备来实现,如超高抛光平坦度(300 mm晶圆中心到边缘的不均匀度<1 nm)、键合晶圆零杂质颗粒、100 nm芯片放置精度等等。

2.混合键合关键工艺

待键合的两片晶圆需历经后道金属化处理、键合电介质的CVD(化学气相沉积)、阻挡层的大马士革沉积和铜填充、轻微铜凹陷的电介质平坦化、等离子激活,完成对准、接合前的准备后,进行室温下的接合以及退火,形成铜焊盘的电互联。

铜/介电材料的CMP(化学机械抛光)是流程中最关键的步骤之一,它决定了要粘合表面的平整度,电介质应具有完全光滑的表面,最重要的是所有铜焊盘上必须具有均匀的凹槽水平。等离子体表面活化步骤的作用是创建几个Si-O-位点,这些位点具有高键合强度(>2.0 J/m2)。活化后使用去离子水冲洗晶圆,紧接着顶部和底部晶圆进行对准,并完成室温下键合。

3.混合键合关键材料

SiCN因其高结合能、良好的防潮性和优异的阻挡铜扩散性能成为首选的键合电介质,其能在长时间内保持亲水行为,并且可以通过工艺调节Si:C:N的比例,从而实现最大的结合强度。

另外,前文提到die-to-wafer键合的难度在于将die粘附到载体晶圆或玻璃上,这其中起到关键作用的是临时键合材料。Brewer Science的CTO表示,临时键合材料可以满足厚度略有不同的芯粒,其粘接层和释放层必须满足混合键合或热压键合所有过程的热预算,并保证不发生任何芯片位移,还需要在释放后没有残留和颗粒。另外,镁光的工作人员认为可以通过用无机薄膜代替用于临时粘合的有机胶水来提高热预算和降低颗粒物水平。

4.混合键合最新进展

现在业界正致力于8层、16层甚至更多层的DRAM(动态随机存取存储器)高带宽存储器(HBM)堆栈。这是一场艰苦的战斗,需要较低热预算的工艺流程来防止DRAM刷新率下降,HBM要求比当前 300-350℃更低的退火温度。最新进展包括:

具有高键合能SiCN的低温沉积工艺;

将平坦度控制在1 nm以内的CMP工艺;

纳米晶镀铜(取向为(111))在200℃下粘合;

通过激光和/或等离子进行晶圆切割;

具有高平行度和< 200 nm精度的die-to-wafer键合设备。

虽然行业已经在集成混合键合工艺及材料方面取得了一定的进展,但业界也将继续寻求支持更加低温的替代方案,以便扩大混合键合技术的应用范围。

(source: Gearing up for hybrid bonding, Semiconductor Engineering)

供稿:战略规划部

审核:肖彬