跟小编一起来看看近期国内外电子材料领域都有哪些最新研究进展吧~

1 科研动态

1、IEEE T. Comp. Pack. Man.:2.5D封装的热机械挑战:翘曲和互连可靠性综述

先进封装技术通过在单个封装基板上安装多个芯片来弥补芯片和封装尺寸之间的差距。使用无源器件的2.5D封装已被广泛采用,容量和性能均有提升。然而,由于硅中介层尺寸较大,2.5D封装在热机械可靠性方面存在挑战。

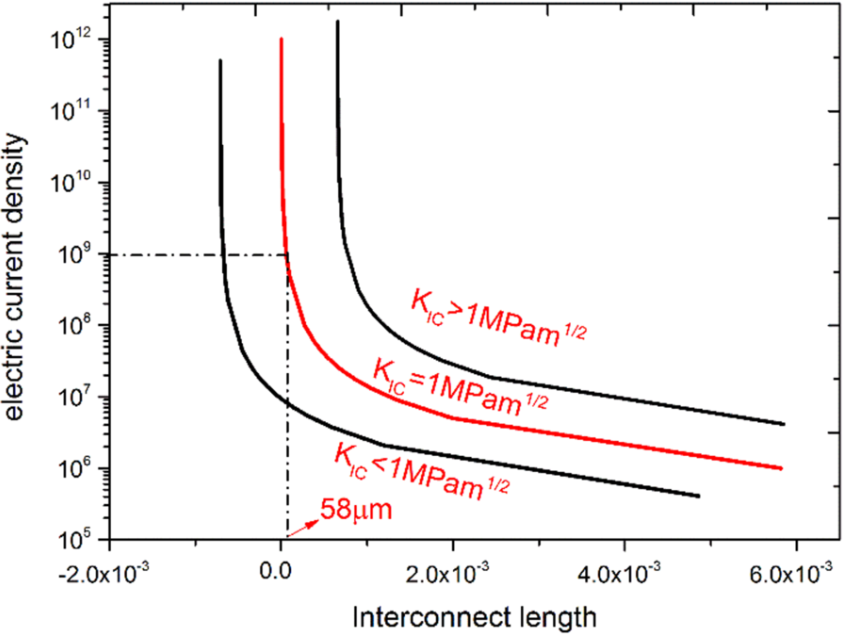

近日,韩国首尔大学的研究人员回顾了学术界和产业界为解决与2.5D封装(特别是硅中介层)相关的热机械挑战所做的一些努力,重点关注翘曲和板级互连可靠性。主要内容包括仿真和测量方法,以评估和预测封装组件的热机械特性,例如翘曲和应变分布以及球栅阵列的疲劳和寿命。另外文章还讨论了材料和几何设计因素的影响。文章最后提出了当前方法和应用前景的挑战。该文章以“Thermo-Mechanical Challenges of 2.5D Packaging: A Review of Warpage and Interconnect Reliability”发表于IEEE T. Comp. Pack. Man.上。

2、IEEE T. Comp. Pack. Man.:使用烧结铜芯片贴装技术提高功率循环测试下的3.3 kV全SiC功率模块的可靠性

利用SiC材料宽带隙特性,使低导通和开关损耗功率模块能够在更高的最大结温下工作。这也意味着更宽的温度范围工作,因此需要更高的功率循环下的服役可靠性。然而,由于碳化硅的硬质材料特性,与传统硅功率模块相比,碳化硅功率模块的功率循环测试结果较差。

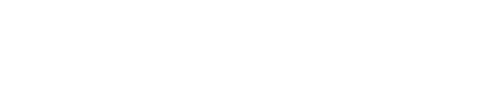

近日,日本大阪大学等机构的研究人员通过用新的铜烧结芯片连接替换传统的焊接芯片连接来解决可靠性问题。本工作开发了一种烧结铜芯片贴装技术,用于3.3 kV 450A全SiC功率模块(最大结温为450℃)。烧结铜芯片贴装改变了功率循环测试的失效模式,由芯片附着层裂纹扩展变成顶部电极上的键合线脱落。功率循环测试显示,与传统富铅焊料连接的SiC模块相比,使用寿命提高了六倍。该文章以“Reliability Improvement of 3.3 kV Full-SiC Power Modules for Power Cycling Tests with Sintered Copper Die Attach Technology”发表于IEEE T. Comp. Pack. Man.上。

图1. 功率循环下烧结银和烧结铜升温变化比较

3、J. Appl. Polym. Sci.:磁场中制备各向异性石墨烯纳米片/环氧树脂复合材料作为有效散热电子封装材料

如今,解决热管理问题是提高各种小型电子设备性能的必要条件。然而,聚合物的固有导热系数非常低,而将高导热纳米填料与聚合物复合可以有效提高聚合物的导热系数。

近日,昆明理工大学的研究人员��究了不同磁场对石墨烯纳米片(GNPs)取向的影响及其对环氧纳米复合材料热导率的影响。通过在制备过程中使用磁场对准的GNP来提高热导率,制备了具有不同GNP含量的各种纳米复合材料样品。结果表明,添加5 wt% GNP的样品的面内热导率达到0.75 Wm−1 K−1,比纯环氧树脂高276.6%,各向异性系数(K∥/K⊥)达到3.3。此外,还进行了温升试验来模拟用作电子封装材料的纳米复合材料的导热系数,结果表明,仅使用较低的填料量,复合材料的面内导热系数得到显著提高。这为导热复合材料的制备提供了思路,并展示出其作为下一代电子设备热管理封装材料的潜力。该文章以“Anisotropy induced in magnetic field in GNPs/epoxy composites used as an effective heat dissipation electronic packaging material”发表于J. Appl. Polym. Sci.上。

图2. (a)三个样品面内热导率比较(相应红外图像作为加热时间的函数)

(b)表面温度随加热时间的变化

(c)各向异性导热片的TCE曲线

4、J. Electron. Packaging:铜互连处电迁移引起的界面断裂

随着集成电路的小型化,电流密度不断增加,从而加剧了电迁移的影响,使其成为微电子故障的最重要原因之一,在先进封装的芯片铜线和再分布层(RDL)中都观察到了这种故障模式。

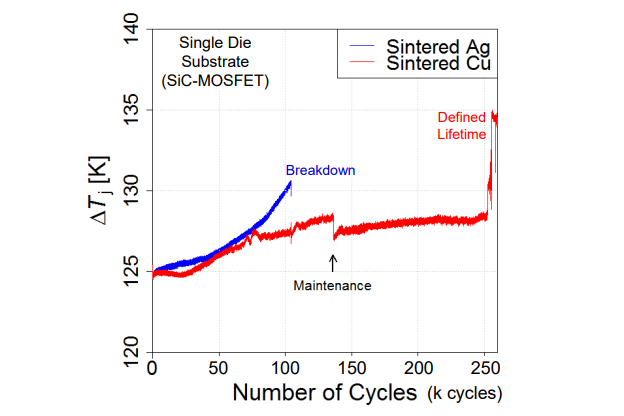

近日,中国工程物理研究院等机构的研究人员深入研究了电迁移引发的铜/电介质界面开裂的失效模型,特别是在铜互连的阳极端。该研究采用连续位错模型来确定铜线内外存在的界面质量扩散引起的应力场。除了阴极或阳极侧的预期拉伸或压缩应力之外,在介电层和铜线的阳极端之间的界面处还发现了异常应力奇异点,这种奇异的应力分布在电迁移的影响下导致了阳极端的介电层的压缩部分中的裂纹。提出的理论预测与实验数据吻合较好,并提出了一种类似于断裂力学应力强度因子的新型失效准则。该文章以“Interfacial Fracture Caused by Electromigration at Copper Interconnects”发表于J. Electron. Packaging上。

图3. 电迁移断裂状态下互连长度与电流密度的关系

2 技术动态

1、关于Chiplet关键标准的简要概述

片上系统(SoC)架构的扩展正在逼近极限,因此通过die-to-die互联的小芯片(chiplet)异构集成封装被认为是重要的突破方向之一,然而chiplet之间的互连技术仍处于初级发展阶段,如何优化chiplet之间的互连受到广泛关注。

因此,建立chiplet之间的互连标准变得十分必要。下面将简要介绍关于chiplet互连的三个标准,这些标准将可能在创建chiplet生态系统方面扮演至关重要的角色。

(1)束线(Bunch of Wires, BoW)

束线互连技术定义了单个封装内的一对die之间的开放的可互操作的物理接口,并指定了一个针对SoC分解进行优化的物理层(PHY),该物理层是形成chiplet多芯片互连的基础。BoW背后的原始互连技术是由Eliyan(一家chiplet互连初创公司)的首席执行官同时也是联合创始人的Ramin Farjadrad开发,并于2018年将其纳入名为“开放计算项目”(Open Compute Project, OCP)中进行标准化。该技术后来被OCP采用为小芯片互连方案。

图4. BoW是一种用于die-to-die(D2D)互连的开放PHY规范,提供并行接口,可以通过有机层压板或先进封装技术实现(图片来源:Eliyan)

(2)通用芯粒互连通道(Universal Chiplet Interconnect Express,UCIe)

2022年3月,一种die-to-die连接的开放行业标准被一个联盟推出,该联盟集结了包括半导体制造、封装厂商以及云服务和IP供应商等共80多家企业。该标准的推出是实现多芯片系统异构集成的重要一步,为chiplet封装概念提供了一个新的设计生态系统。

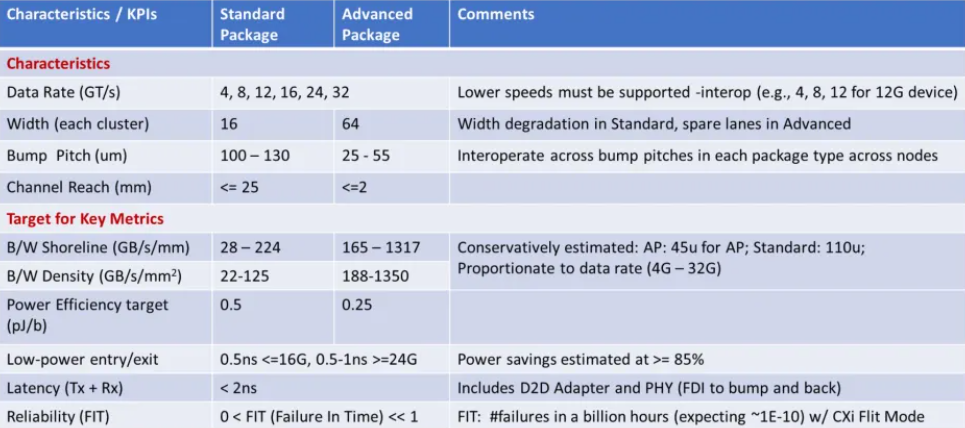

UCIe在封装级别提供了一种“即插即用”的互连标准,该标准使不同厂商用不同工艺技术制造的die之间的互操作性效率更高。该标准是基于BoW互连中相同的信号和时钟方案以及架构基础,目前UCIe 1.1可以使用。

图5. UCIe定义了封装中chiplet的关键性能指标(图片来源:UCIe)

(3)高带宽存储器(High Bandwidth Memory, HBM)

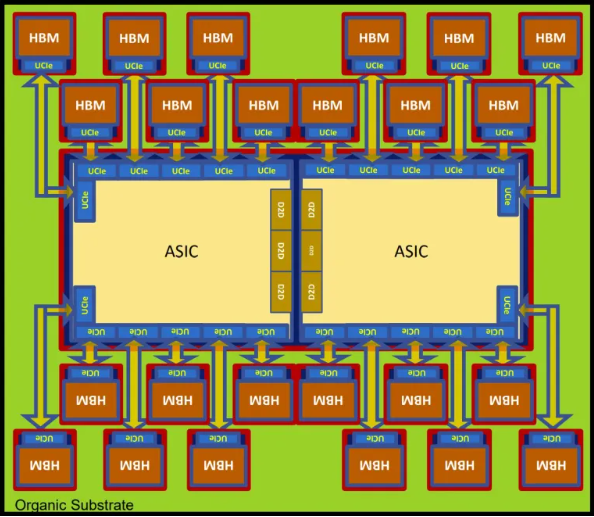

虽然确切来说,HBM不算chiplet标准,但HBM能够将大量储存芯片封装到更小的空间中,因此成为了chiplet设计中的重要组成部分。HBM采用硅通孔(TSV)技术在各层储存芯片中提供垂直互连通道,使得存储芯片实现堆叠。HBM最初的设计目的是减少存储器和处理器之间的数据传输距离,用于数据中心和云计算等计算密级型应用。但由于其垂直堆叠DRAM芯片的能力,与chiplet设计具有高度相关性,这也是为什么目前一些新的chiplet解决方案支持UCIe和HBM协议。

图6. 最初为高性能计算(HPC)应用程序设计的HBM在chiplet设计生态系统中发挥着关键作用(图片来源:Eliyan)

(source: a sneak peek at chiplet standards, EDN)