1

科研动态

1、IEEE T. Comp. Pack. Man.:2.5D集成封装嵌入式微通道散热器研究

研究人员普遍认为,温度完整性是开发2.5D/3D集成封装系统最具挑战性的障碍之一。

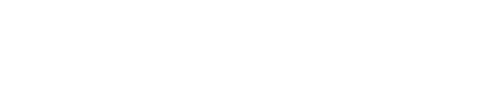

近日,浙江省大规模集成电路设计重点实验室的研究人员设计了一种用于2.5D封装热管理、带有硅通孔(TSV)蚀刻微引脚鳍片的嵌入式微通道散热器(EMCHS),并开发数值模拟模型来估计EMCHS和封装的热性能和机械性能。首先验证了模型的准确性,然后提出了一些模型简化手段以降低模型的阶数,从而提高仿真计算的时间并节省资源成本。通过进一步在功率和散热能力之间权衡,提出了一种EMCHS的最佳设计方法。该方法采用灰色关系分析来寻求最优设计参数,并采用仿真模型进行快速性能评估。仿真结果表明,优化后的EMCHS和2.5D封装在散热能力和机械可靠性方面均有显著提高。该工作对2.5D集成封装的散热设计提供了参考。该文章以“Investigation on Embedded Microchannel Heatsink for 2.5-D Integrated Package”发表于IEEE T. Comp. Pack. Man.上。

图1. 单个微通道的温度与应力分布:(a)不具有、(b)具有优化排列的微引脚

论文链接:DOI:10.1109/TCPMT.2023.3292005

2、J. Appl. Polym. Sci.:用于柔性覆铜板的具有高剥离强度和优异焊接耐热性能的环氧胶粘剂

柔性覆铜板(FCCL)通常由铜箔、环氧粘合剂和聚酰亚胺(PI)薄膜组成,被广泛用作柔性印刷电路板的基板材料。

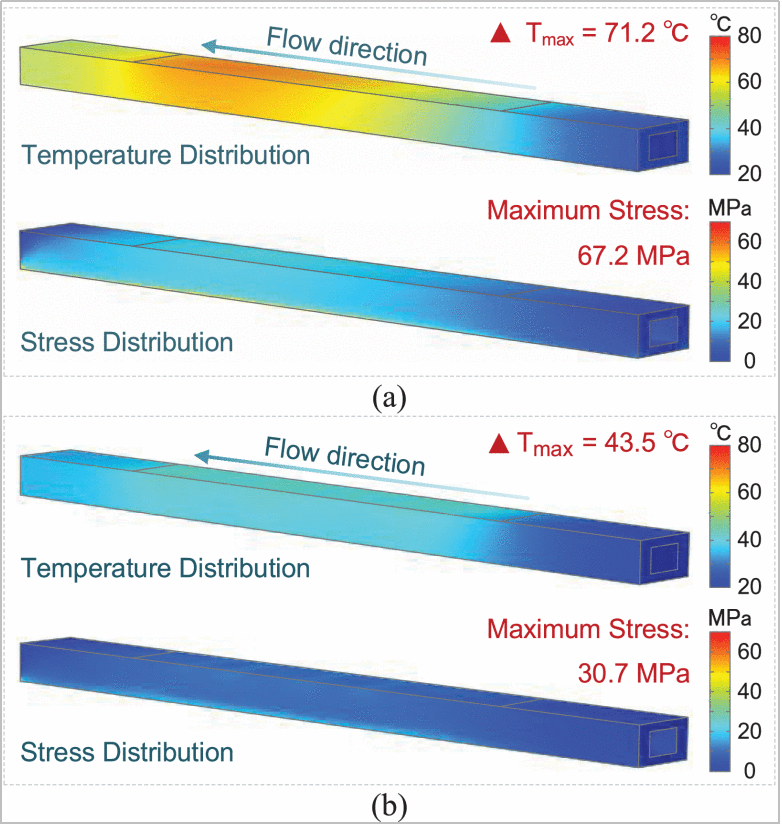

近日,华南理工大学的研究人员采用羧基封端丙烯腈-丁二烯(CTBN)和四种固化剂制备了改性环氧胶粘剂,并且用等离子体处理PI,以提高FCCL的剥离强度。结果表明,当环氧胶黏剂加入30份的CTBN进行增韧、PI薄膜用氮等离子体处理后,改性环氧胶粘剂和FCCL的综合性能最好。改性环氧胶粘剂的冲击强度为39.32 kJ m−2(比未改性的高149.7%),160℃下凝胶化时间为330 s 。FCCL的剥离强度为1.29 kgf cm−1,高于指标要求。该方法为扩展FCCL在需要更高剥离强度领域的应用提供了一种新途径。该文章以“High peel strength and excellent solder heat-resistance epoxy adhesive for flexible copper clad laminate”发表于J. Appl. Polym. Sci.上。

图2. 不同CTBN含量改性的环氧胶粘剂的机械性能:(a)拉伸强度,(b)冲击强度,(c)弯曲强度,(d)弯曲模量。

论文链接:https://doi.org/10.1002/app.54596

3、 Mat. Sci. Semicon. Proc.:关于TSV绝缘衬里替代材料的综述

现今,3D集成是芯片领域被公认的最有发展前景的方向。3D集成背后的核心技术是硅通孔(TSV)结构,它为芯片提供垂直电气互连。绝缘衬里是保证TSV功能的关键部件,对电气特性和热机械可靠性产生重要影响。然而,由于集成和封装形式趋于复杂化,传统绝缘衬里面临着持续的挑战,因为TSV的直径变得更小、纵横比变得更高。因此,需要不断探索和测试新型绝缘衬里方法,以满足严格的要求。

近日,上海交通大学的研究人员发表综述文章,对绝缘衬里进行了全面的比较和总结,包括次常压化学气相沉积(SACVD)和等离子体增强化学气相沉积(PECVD)等传统方法,以及原子层沉积(ALD)、气隙(air-gap)、气相沉积聚合物和湿沉积聚合物等新型替代方法。根据其特定的性能特性(例如覆盖性、电气特性和热机械可靠性)讨论了每种方法的优缺点,这些性能对与TSV实现正常功能至关重要。对不同绝缘衬里的评估将有助于研究人员更好地理解这些方法,并根据他们的特定需求和要求做出合理决策。该综述以“Alternative insulation liners for through-silicon vias: A comprehensive review”���表于Mat. Sci. Semicon. Proc.上。

表1. 不同绝缘衬里工艺的比较

论文链接:https://doi.org/10.1016/j.mssp.2023.107726

4、J. Electron. Packaging:电子封装中多尺度结构弹塑性问题的自动有限元法-边界元法耦合方法

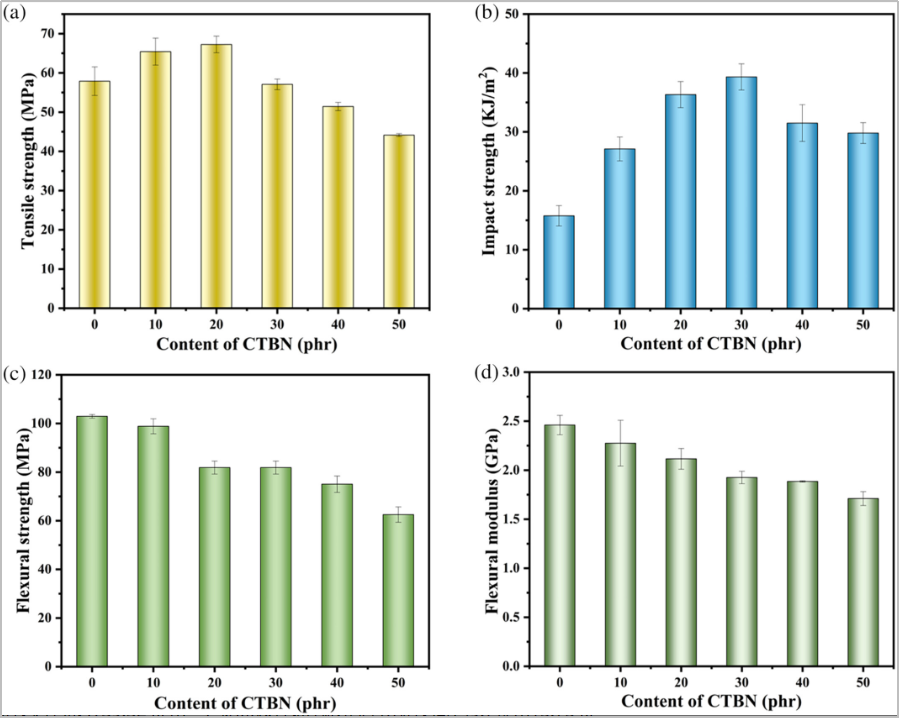

有限元在电子封装结构的仿真分析中起着重要作用。然而,由于电子封装中的多尺度结构,数值模型必须离散化成大量的单元,以确保计算精度,这无疑增加了计算时间和成本。为了解决这个问题,研究人员扩展了边界元方法,用于分析电子封装问题。

近日,北京科技大学等机构的研究人员介绍了一种用于多尺度电子封装结构弹塑性分析的有限元和边界元耦合方法。基于有限元-边界元(FE-BE)耦合算法,开发了一种针对弹性问题,自动实现ABAQUS(一种有限元模拟软件)与自写弹性BE码耦合的程序。首先,在有限元-边界元混合模型中,采用自行编写的BE程序对界面处的有效刚度和有效力进行了评估。然后,使用ABAQUS中的用户子程序(UEL)将获得的有效刚度和有效力组装成全局有限元公式。有限元理论可以对具有塑性变形、应力集中等情况的结构进行数值模拟,边界元法适用于具有大型结构的线弹性域。与目前可用于多尺度电子封装结构的分析方法相比,该方法具有以下几个关键优势:(1)ABAQUS强大的前处理和后处理能力;(2)精度更高;(3)减少计算成本和时间;(4)可通过使用边界元作为补充来求解具有无限可拓性的系统。该方法被证明可以处理电子封装中多尺度结构的相关问题。该文章以“An Automatic Finite Element Method-Boundary Element Method Coupling Method for Elastic–Plastic Problems of Multiscale Structures in Electronic Packaging”发表于J. Electron. Packaging上。

图3. 耦合方案流程图

论文链接:https://doi.org/10.1115/1.4055125

2

技术动态

1、近期Chiplet和异构集成的进展和趋势

摩尔定律正逼近物理极限,减小片上系统(SoC)的特征尺寸变得越来越困难,且成本高昂。近年来,国际巨头们均着力于发展Chiplet设计和异构集成封装技术,即把SoC划分成不同的功能区域,实现更好性能的同时减少成本。

(1)AMD

2017年,加州大学圣芭芭拉分校与ADM公司发表论文,展示了AMD未来的chiplet设计和异构集成封装,即小芯片通过TSV中介层堆叠在一起,形成一种3D集成。

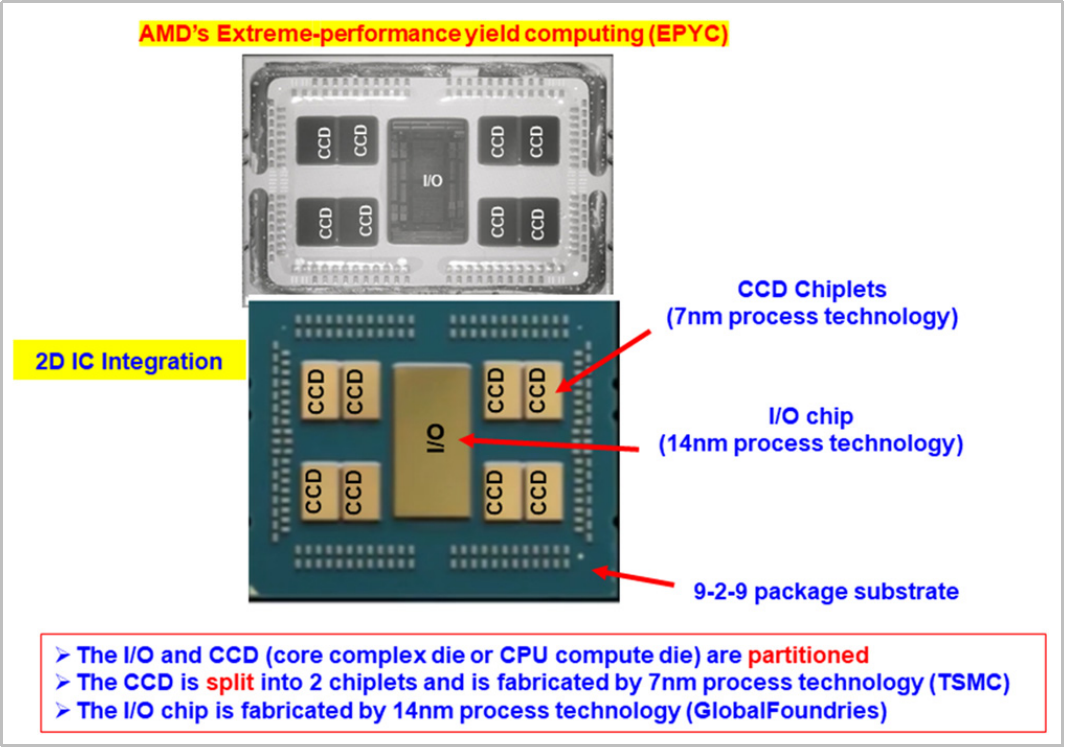

a)EPYC(Extreme-Performance Yield Computing)

对于高性能服务器和处理器等I/O的密度十分高的场景,先进制程对于提高I/O密度十分有限且造价昂贵。2019年年中,AMD推出了第二代EPYC 7200系列,代号为Rome,核心数量增加到64个,如图4所示,该技术采用一种9-2-9封装,I/O和CPU分别被分为多个小芯片,CPU核心采用7 nm制程,I/O芯片采用14 nm制程。AMD保持封装尺寸和引脚排列不变,同时核心数量从第一代的4个增加到第二代的9个,因此需要更紧密的芯片/封装的协同设计。

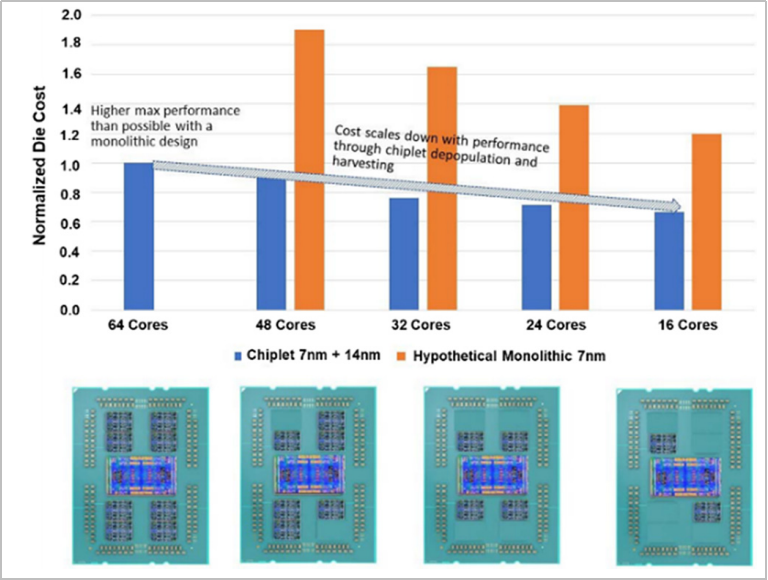

第二代EPYC的性能与成本对比如图5所示,核心数量越多意味着成本更高,但是采用chiplet设计能节约近一半的成本,随着核心数量增多,chiplet设计的成本优势越发明显。

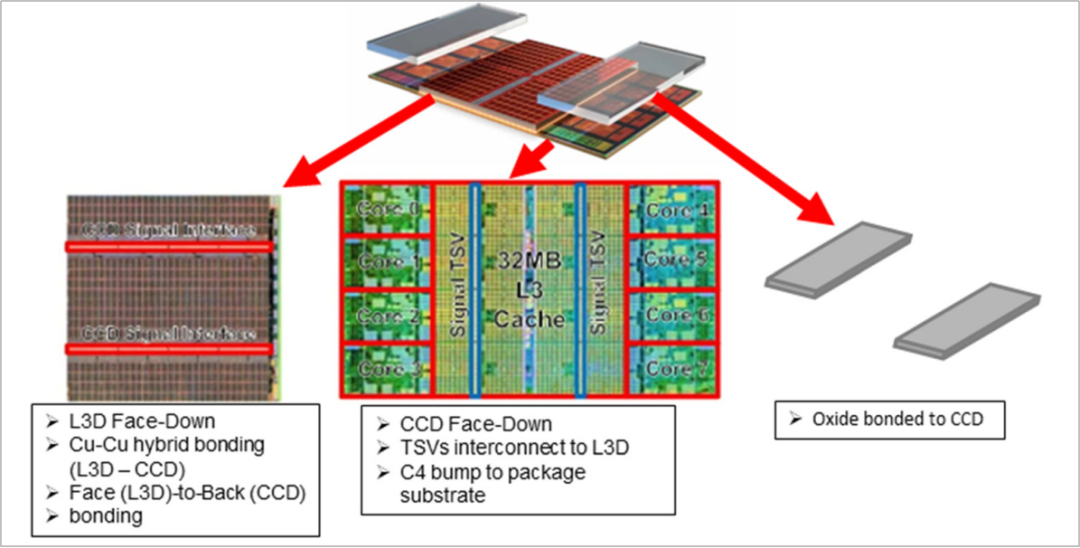

b)AMD 3D V-Cache

在2022年,AMD发布了他们的3D V-Cache chiplet设计,如图6所示。该结构由底部的计算芯片、顶部的静态RAM和用于平衡结构并提供散热路径的结构芯片组成。底部计算芯片是采用台积电7 nm工艺技术制造的“Zen 3”CPU,顶部是同样由7 nm工艺制造的扩展L3芯片。顶部芯片面朝下与底部芯片通过Cu-Cu混合键合。

a)Intel’s Foveros技术

Intel在2018年12月和2019年7月分别发布了Foveros技术和全向互联(ODI)技术,如图7所示。TSV中介层是带有CMOS(互补金属氧化物半导体)器件(有源中介层),有源TSV中介层位于SoC或chiplet的下方,与小芯片或SoC通过热压键合。

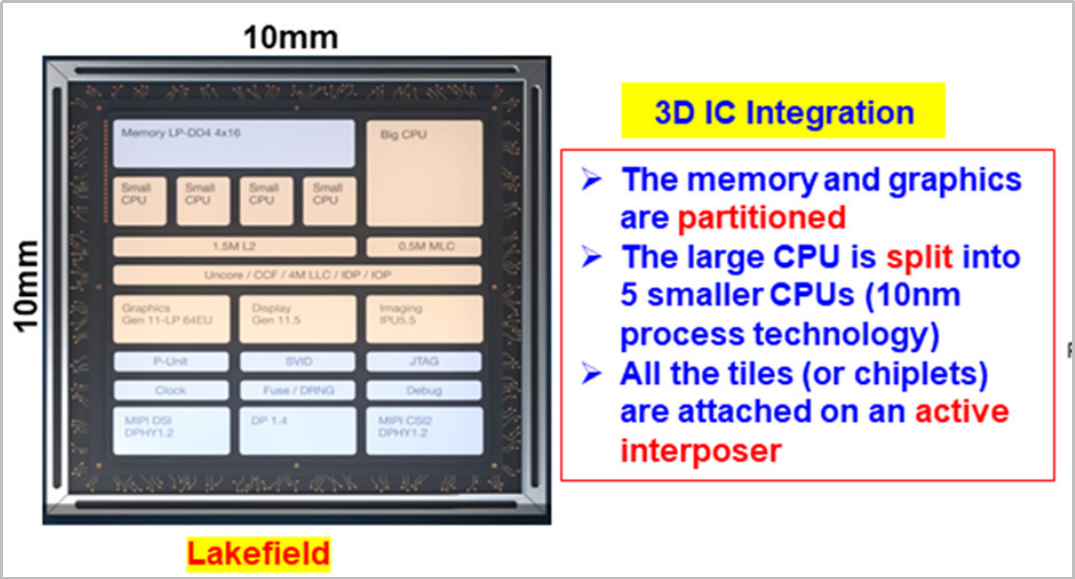

b)Intel’s Lakefield

2020年7月,基于Foveros技术,英特尔推出笔记本电脑处理器“Lakefield”。如图8所示,SoC被划分为CPU、GPU、LPDDR4等多个部分,并且CPU继续被分割成1大+4小CPU,然后使用CoW(chip on wafer)工艺使小芯片面对面键合(堆叠)在有源TSV中介层。小芯片是10 nm工艺制造,基底芯片采用22 nm工艺。这是首个大批量制造的3D chiplet集成,并用于笔记本电脑等移动产品。

图8. Intel’s Lakefield示意图

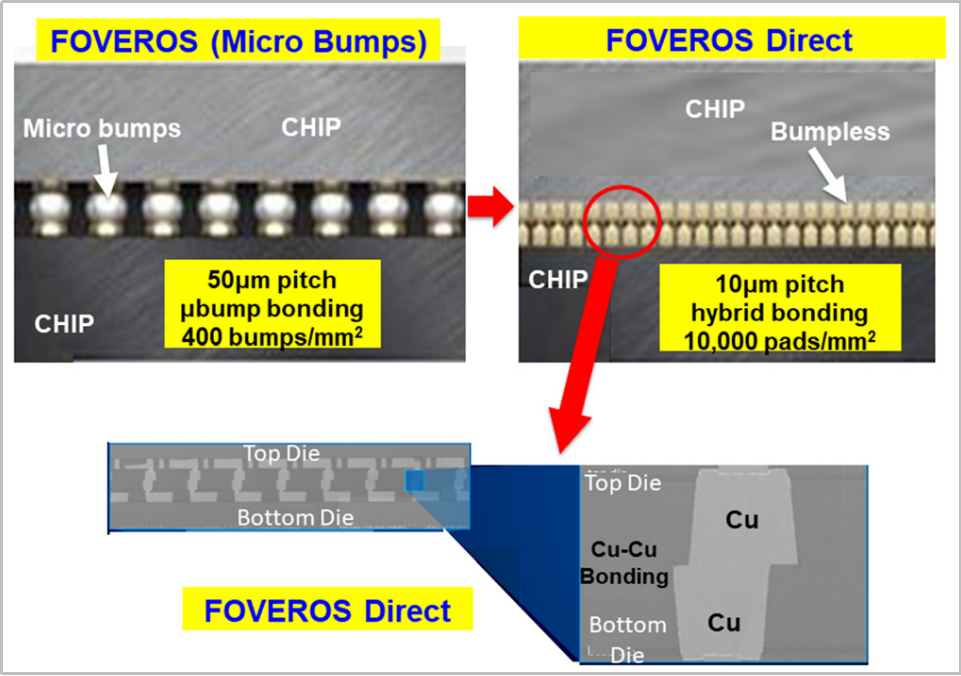

c)Intel’s Foveros-Direct

2020年8月13日,Intel发布采用Cu-Cu键合的Foveros-Direct技术。通过混合键合代替凸块,可将间距从Lakefield的50 μm降至10 μm。

图9. Intel’s Foveros-Direct(Cu-Cu混合键合)

(3)台积电

a)3D Fabric

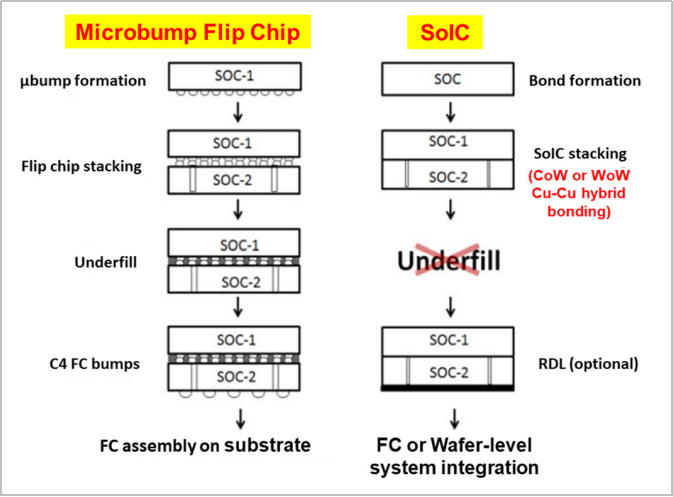

2020年8月,台积电宣布了他们的3D Fabric技术,可应用于手机、高性能计算、汽车和物联网等领域。3D Fabric的核心技术是SoIC(system on integrated chips),该技术由台积电于2018年发布。3D Fabric可以通过CoW(chip on wafer)和WoW(wafer on wafer)提供灵活的芯片级chiplet设计和集成,与传统微凸块键合相比,混合键合SoIC具有更好的电气性能和密度,以及更好的热性能。

图10. 台积电SoIC与倒装封装对比

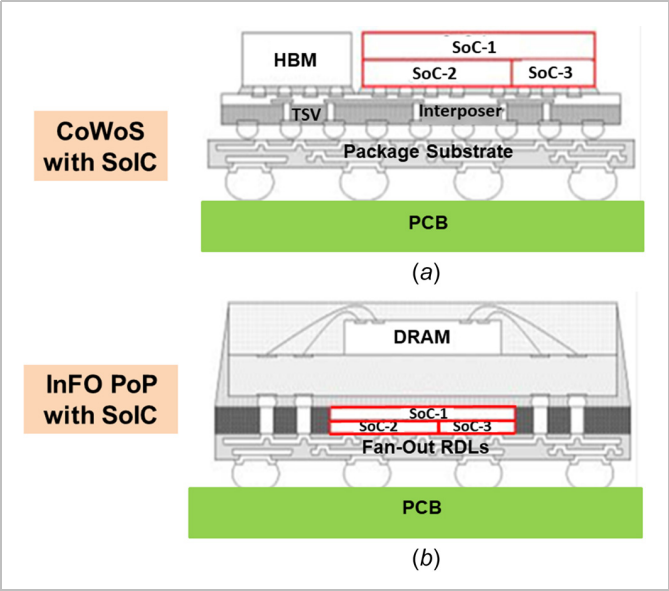

b)台积电CoWoS和InFO POP

在3D后端集成方面,CoWoS(chip on wafer on substrate)封装技术提供了极高的计算性能和高宽带内存,可满足高端服务器的高速运算需求;InFO(集成扇出)提供了存储器-逻辑、逻辑-逻辑、PoP(package-on-package)等应用。

图11. 在异构集成前,使用SoIC进行小芯片的堆叠(a)采用SoIC的CoWos、(b)采用SoIC的InFO PoP

4. Chiplet设计和异质集成封装的优缺点

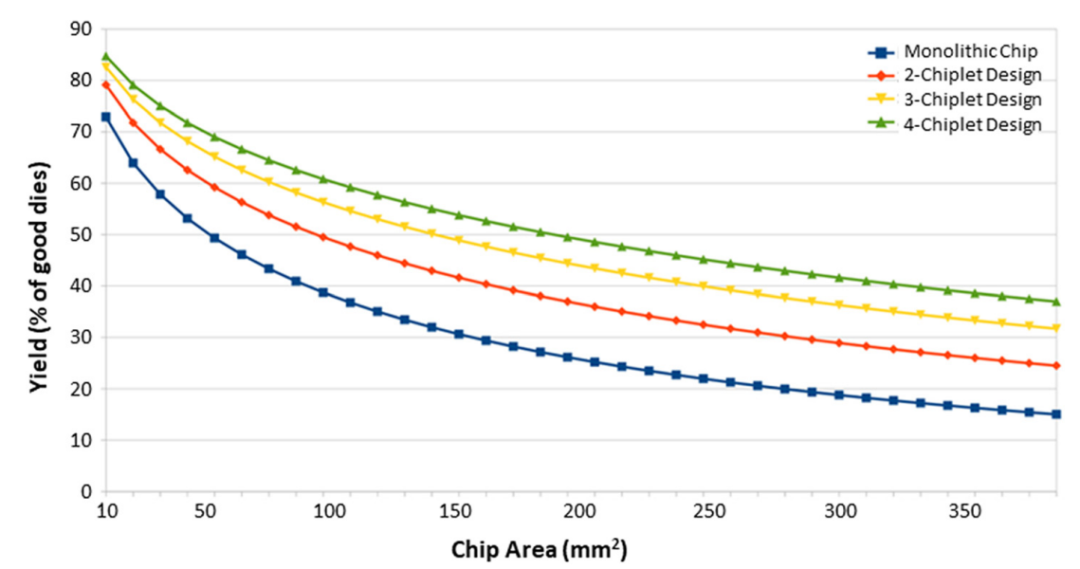

与SoC相比,chiplet设计的主要优势在于可以提高良率、降低成本。图12显示了整片设计和分别拆分成2、3、4个小芯片的整体芯片产量比较。可以看出芯片尺寸越小,良率就越高,最终产量提高,从而可以转化为更低的成本,同时加快产品迭代时间。此外,由于分散成小芯片,可以提高整体的散热效率。

图12. 芯片整体良率与芯片尺寸的关系

然而,由于芯片分区,毫无疑问将增大芯片面积,因此反过来对封装整体设计提出更高要求,以实现更小体积。同时,chiplet要求更多、更高密度的封装互联,对封装材料提出了更高的要求。

(Source:John H. Lau, Recent Advances and Trends in Chiplet Design and Heterogeneous IntegrationPackaging, ASME Journal of Electronic Packaging, Vol 146, 010801, 2024.)